# **MBUS Interface Specification**

# **MBUS Module Design Guide**

#### © 1990, 1991, 1992, 1993, 1994, 1995, 1996, 1997 SPARC International Inc.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the copyright owners.

# The manual pages for socket functions are @ 1992, 1993 The Regents of the University of California. All rights reserved

Includes material copyrighted by UNIX System Laboratories, Inc., a subsidiary of SCO, Inc. Reprinted with permission.

The SPARC Compliance Definition 2.3 is published and printed by SPARC International.

Any comments relating to the material contained herein may be submitted to:

SPARC International Inc. 3333 Bowers Ave., Suite 280 Santa Clara, CA 95054-2913 TEL: (408) 748-9111 (Ext 228) FAX: (408) 743-9777 URL: www.sparc.org ATTN: Ghassan Abbas (abbas@sparc.org)

#### Trademarks

SPARC® is a registered trademark of SPARC International, Inc.

SPARCstation<sup>TM</sup> is a trademark of SPARC International, Inc.

Products bearing SPARC® trademarks are based on an architecture developed by Sun Microsystems, Inc.

ONC<sup>™</sup> and SunOS<sup>™</sup> are trademarks of Sun Microsystems, Inc.

NFS® is a registered trademark of Sun Microsystems, Inc.

UNIX® and OPEN LOOK® are registered trademarks of UNIX System Laboratories, Inc.

The X-Window System<sup>™</sup> is a trademark of Massachusetts Institute of Technology.

OSF/Motif<sup>™</sup> is a trademark of the TOG (X/Open + Open Software Foundation, Inc).

All other products or services mentioned in this document are identified by the trademarks or service marks of their respective companies or organizations. SPARC International, Inc. disclaims any responsibility for specifying which trademarks are owned by which companies or organizations.

# **Table Of Contents**

# Table Of Contents

# **Chapter 1-MBus Interface Specification**

| Introduction                                                  | 2-1  |

|---------------------------------------------------------------|------|

| Features                                                      |      |

|                                                               |      |

| MBus Levels                                                   |      |

| Definitions                                                   |      |

| Basic Assumptions for Level 2                                 | 2-4  |

| Signal Definition                                             |      |

| Physical Signal Summary                                       |      |

| Physical Signal Descriptions                                  |      |

| Multiplexed Signal Summary                                    |      |

| Multiplexed Signal Descriptions                               |      |

| MBus Transactions                                             |      |

| Semantics                                                     | 2-11 |

| Level 1 Transaction Types                                     |      |

| Additional Transaction Types for Level 2                      |      |

| Acknowledgment Cycles                                         |      |

| Arbitration                                                   |      |

| Arbitration Principles                                        |      |

| Arbitration Protocol                                          |      |

| MBus Configuration Address Map                                |      |

| MBus Electrical Characteristics                               |      |

| MBus Electrical Principles                                    |      |

| Signal Grouping                                               |      |

| Definitions                                                   |      |

| Timing Reference Diagram                                      |      |

| Clocks                                                        |      |

| Level-1 and Level-2 Clock Characteristics (Ta = 0-70C)        |      |

| Level-1 AC Characteristics (MAD and Control) ( $Ta = 0.70C$ ) |      |

| Level-2 AC Characteristics (MAD and Control) ( $Ta = 0.70C$ ) |      |

| Level-1 and Level-2 AC Characteristics(Scan) ( $Ta = 0.70C$ ) |      |

| Level-1 and Level-2 DC Characteristics (Ta = 0-70C)           |      |

| General Electrical Topics                                     |      |

| Mechanical Specifications                                     |      |

| MBus Connector                                                |      |

| MBus Connector Pin-out                                        | 2-27 |

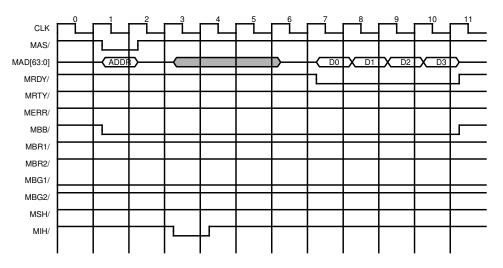

| Timing Diagram Examples                                       |      |

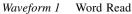

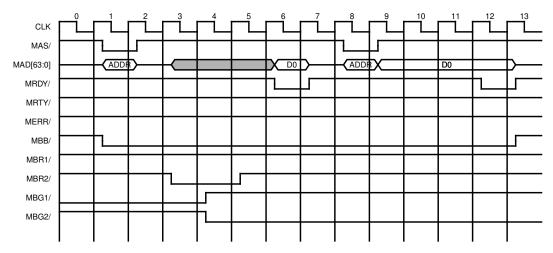

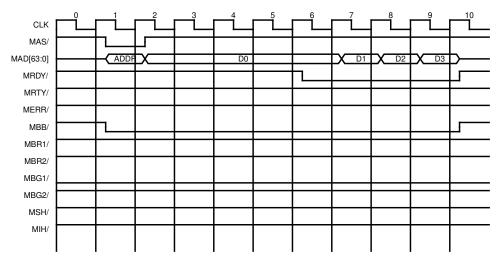

| Word Read                                                     |      |

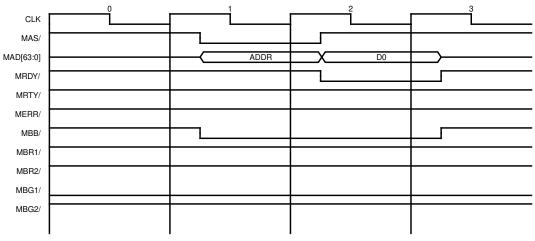

| Word Write                                                    | 2-29 |

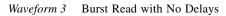

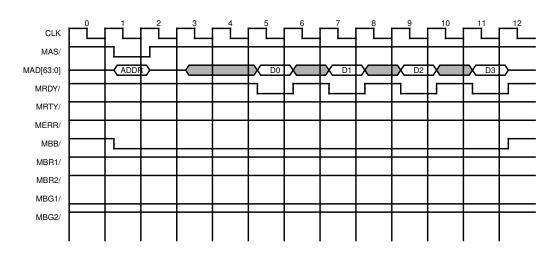

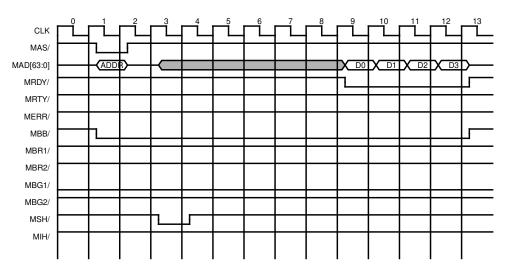

| Burst Read with No Delays                                     |      |

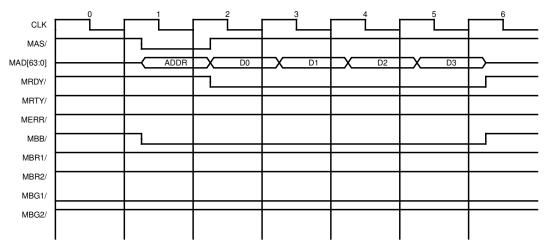

| Burst Read with Delays                                        |      |

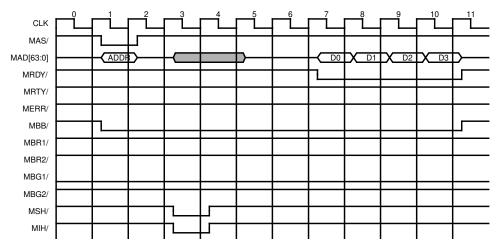

| Burst Write with No Delays                                    |      |

| Burst Write with Delays                                       |      |

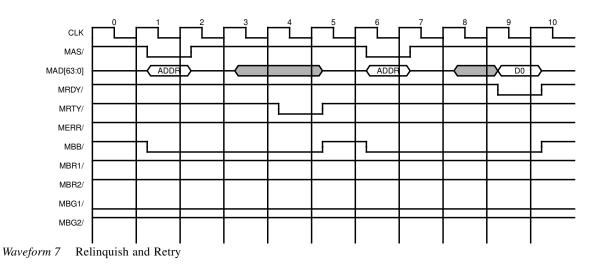

| Relinquish and Retry                                          |      |

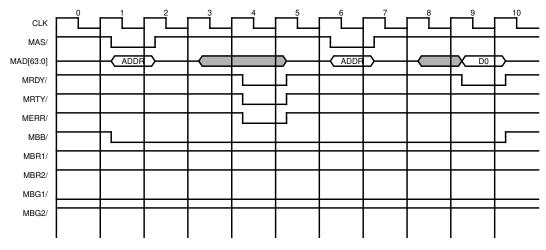

| Retry                                                         |      |

| •                                                             |      |

|           | ERROR1 (Bus Error)                                | 2-32 |

|-----------|---------------------------------------------------|------|

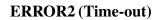

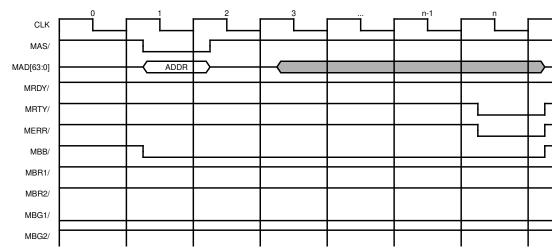

|           | ERROR2 (Time-out)                                 | 2-33 |

|           | ERROR3 (Uncorrectable)                            | 2-34 |

|           | Initial Bus Arbitration                           |      |

|           | Arbitration from Master 1 to Master 2             | 2-35 |

|           | Arbitration with Multiple Requests                |      |

|           | Locked Cycles                                     |      |

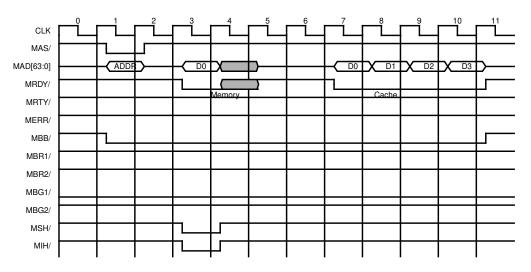

|           | Coherent Read of Shared Data                      |      |

|           | Coherent Read of Owned Data (long-latency memory) |      |

|           | Coherent Read of Owned Data (fast 1)              |      |

|           | Coherent Write and Invalidate.                    |      |

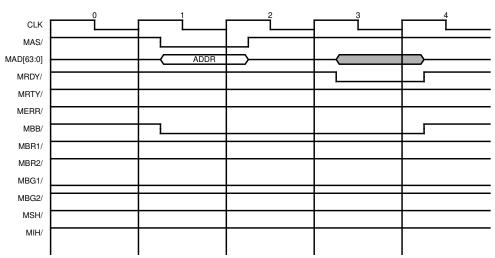

|           | Coherent Invalidate                               |      |

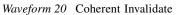

|           | Coherent Read and Invalidate (of Shared Data)     |      |

|           | Coherent Read and Invalidate (of Owned Data)      |      |

| Supr      | lement A                                          |      |

| Supp      | MBus Port Register Assignments                    |      |

| Supr      | lement B                                          |      |

| Supp      | Notes to Implementors                             |      |

|           | Memory Controllers                                |      |

|           | I/O Adapters                                      |      |

|           | Reflective Memory Support                         |      |

|           | Second-Level Cache Issues                         |      |

|           |                                                   |      |

|           | Timing of MSH/ and MIH/<br>Compatibility Issues   |      |

| Chantan 1 | 1 7                                               | 2-44 |

| -         | -MBus Module Design Guide                         |      |

| Intro     | duction                                           |      |

|           | Purpose                                           |      |

|           | Scope                                             |      |

|           | Reference Documents                               |      |

|           | MBus Modules                                      |      |

|           | MBus Platforms                                    |      |

| Elect     | rical Specifications                              |      |

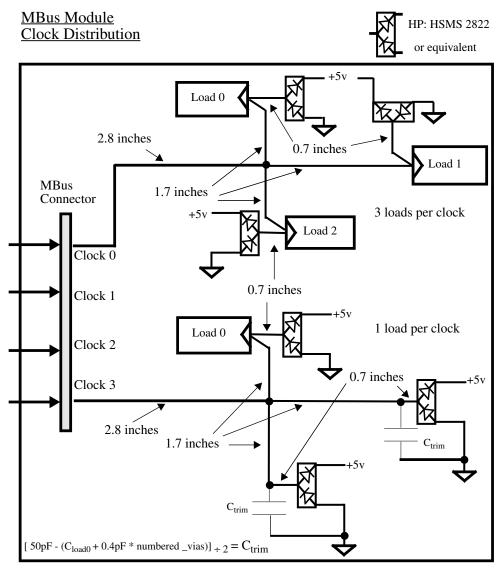

|           | Clocks                                            |      |

|           | MBus Chip Timing Specifications                   |      |

|           | Miscellaneous Timing Issues                       |      |

| Gene      | rating MBus Chip-level Timing Specifications      | 2-6  |

|           | Clock to Output Delay                             | 2-6  |

|           | Bused Control: MAS                                | 2-7  |

|           | MAD: MAD60                                        | 2-7  |

|           | Point to Point Control: MBG1                      | 2-8  |

| Cloc      | k-to-Output Hold                                  | 2-8  |

|           | Bused Control: MBB                                |      |

|           | MAD: MAD34                                        | 2-9  |

|           | POINT TO POINT CONTROL; MBG3                      | 2-9  |

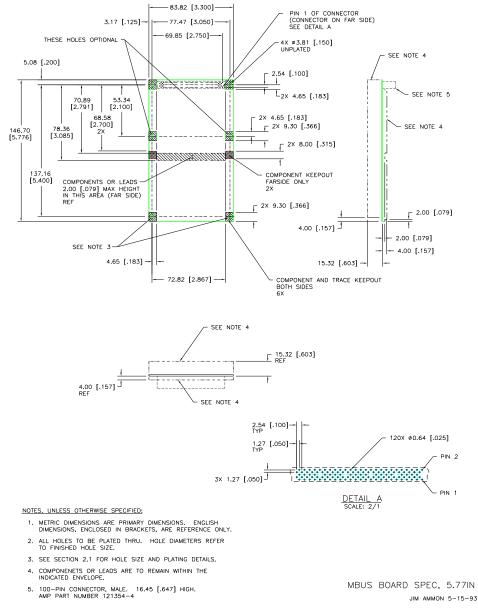

| Mecl      | nanical Specifications                            |      |

|           | MBus Connector                                    |      |

|           |                                                   |      |

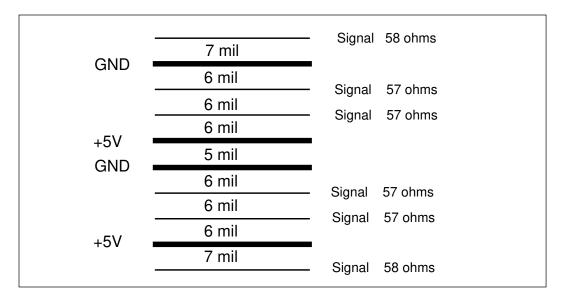

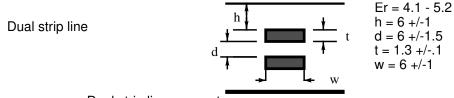

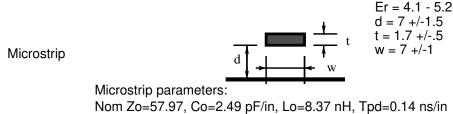

| PCB Board Construction and Routing                   | 2-12 |

|------------------------------------------------------|------|

| PCB Construction.                                    | 2-12 |

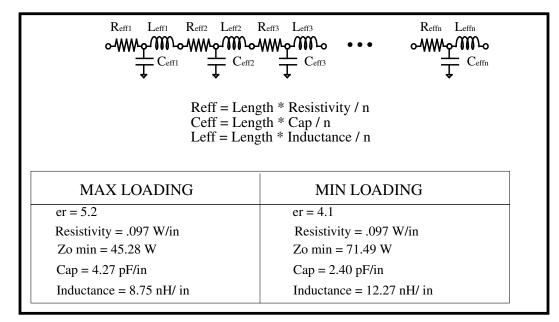

| SPICE Model                                          | 2-12 |

| Routing                                              | 2-13 |

| Routing of the MBus (Memory/address and Control)     | 2-15 |

| Power and Environment Considerations                 | 2-16 |

| Power                                                | 2-16 |

| Heat Removal                                         | 2-17 |

| Environmental                                        | 2-17 |

| Testability Issues                                   | 2-17 |

| Testability of Interconnects                         | 2-17 |

| MBus SCAN Pin Definitions                            | 2-17 |

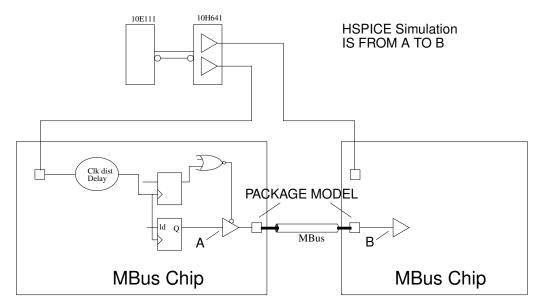

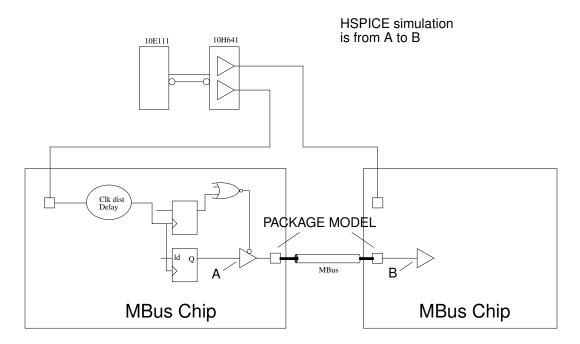

| Supplement B1 - Evaluation of MBus Propagation Delay | 2-18 |

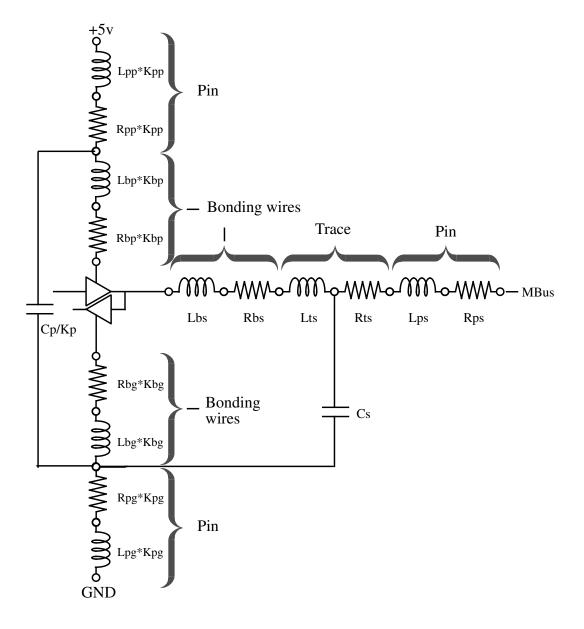

| Creation of Pcb Model for Module                     | 2-19 |

| Creation of Package Model for Ic                     | 2-19 |

| Creation of Driver Subcircuit File                   | 2-19 |

| Update Path in .LIB STATEMENT                        | 2-19 |

| Edit PCB Parameters                                  | 2-19 |

| Run HSPICE                                           | 2-19 |

| Evaluate Results                                     | 2-19 |

| Supplement B2 - HSPICE Parameters                    | 2-20 |

| Equivalent Pin Grid Array Circuit                    | 2-21 |

| Sample Model Parameters                              | 2-21 |

| Supplement B3 - Simulation Parameters                | 2-25 |

| Supplement B4 - PACKAGE MODEL, FILE LISTING          | 2-26 |

| Supplement B5 - MODEL FOR MODULE PCB                 | 2-27 |

| Supplement B6 - MBus Module Mechanical Drawings      | 2-30 |

| Index                                                |      |

# **Chapter 1-MBus Interface Specification**

# Introduction

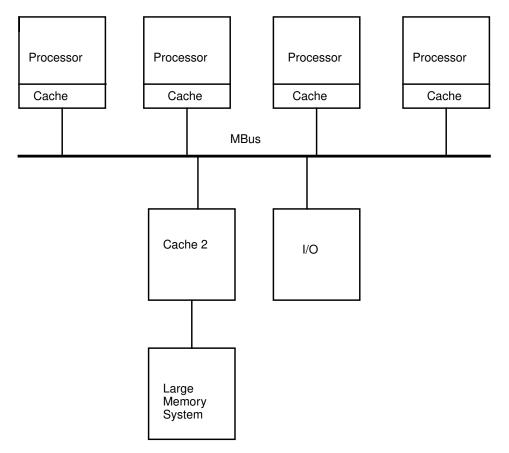

The SPARC<sup>TM</sup> MBus is a private, high-speed interface which connects SPARC<sup>TM</sup> processor modules to physical memory modules and I/O modules. The specification could be thought of as a generic integrated circuit pin interface specification. The interface is not intended for use as a general expansion bus on a system backplane spanning numerous boards. Rather, it is intended to operate in a carefully controlled geographical area with the interconnect and associated circuitry located on only one printed wiring board. Modules consist of one or more integrated circuits, one (or more) of which contain the MBus interface.

The two major goals of MBus are that it be simple and that it be compatible with CMOS technology. Simplicity is achieved by having only a few well-specified transactions with a minimum of options using a small set of signals. CMOS compatibility is covered by the electrical specifications and protocols.

## Features

- fully synchronous, nominally 40 Mhz

- circuit switched

- 64-bit, multiplexed address and data

- 64 gigabytes of physical address space

- multiple-master

- centralized arbitration, reset, interrupt distribution, and clock distribution

- overlapped arbitration with "parking"

- shared memory multiprocessor(MP) signals and transactions

- supports a write-invalidate type of cache consistency protocol

### **MBus Levels**

The complete MBus Specification has two levels of compliance, Level 1 and Level 2. Level 1 includes the basic MBus signals and transactions needed to design a complete uniprocessor system. Level 2 introduces additional signals and transactions needed to design a cache coherent, shared-memory multiprocessor.

A device which conforms to Level 1 of the Specification will be classified as a level 1 device while those devices conforming to Level 2 of the Specification shall be referred to as level 2 devices. Level 1 devices will function properly in a level 2 system. Since one of the intents of MBus is to allow for modular SPARC solutions, care has been taken to ensure all modules in an MBus system can be compatible.

#### Level 1 Overview

The Level 1 MBus supports two transactions, Read and Write. These transactions simply read or write a specified SIZE of bytes from a specified physical address. These transactions are supported using a subset of the MBus signals, namely a 64-bit multiplexed address/data bus (MAD[63:0]), an address strobe signal (MAS/), and an encoded acknowledge on three signals (MRDY/, MRTY/, MERR/). Additional Level 1 signals support arbitration for modules (MBR/, MBG/, MBB/) as well as interrupt inputs (IRL[3:0]), interrupt output (INTOUT/), reset (RSTIN/), asynchronous errors (AERR/), scan (SCANDI, SCANDO, SCANCLK, SCANTMS1, SCANTMS2) and module identification (ID[3:0]). The MBus reference clock (CLK) completes the signal requirements for a Level 1 system.

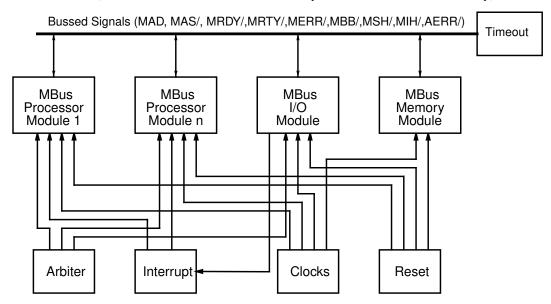

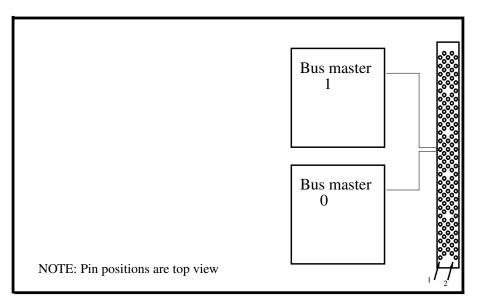

It is assumed that there are central functional elements to perform reset, arbitration, interrupt distribution, timeout, and MBus clock generation as shown in Figure A-1. All modules with the exception of processor and Timeout modules accept an ID[3:0] input which is used as an aid to system configuration. Also the binary value input to a module on ID[3:0] is output as part of MAD[63:0] during the address phase of every transaction.

#### Level 2 Overview

The Level 2 MBus includes all Level 1 transactions and signals and adds four transactions and two signals to support cache coherency. This is to facilitate the design of shared-memory multiprocessor systems. In Level 1, details of the caches inside modules are not visible to the MBus transactions. This changes with Level 2, where many aspects of the caches are assumed as part of the new MBus transactions. To participate in sharing between processor caches on an MBus using Level 2 transactions, a cache must minimally support a "write-back" policy, an "allocate" policy on write misses, and have a block or sub-block size of 32 bytes. Cache lines are assumed to have at least five states (invalid, exclusive clean, exclusive dirty, shared clean, and shared dirty).

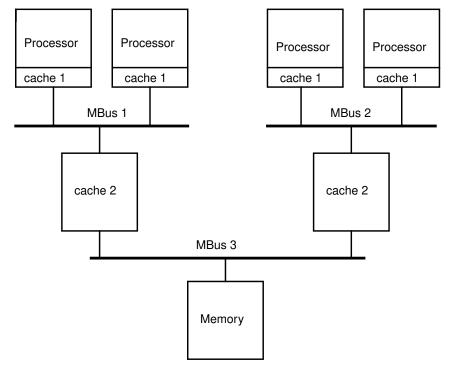

Figure A-1 MBus System Elements and Their Connectivity.

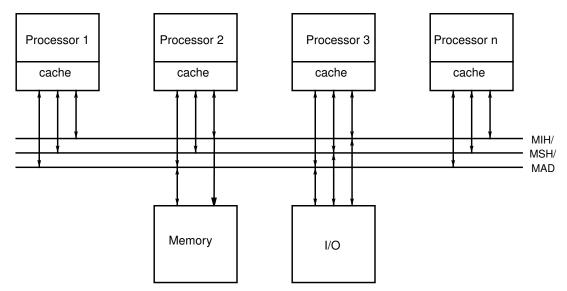

The additional transactions present in Level 2 systems are Coherent Read, Coherent Invalidate, Coherent Read and Invalidate, and Coherent Write and Invalidate. The two additional signals are Shared (MSH/) and Inhibit (MIH/). Coherent transactions, with one rare exception (Coherent Write and Invalidate used with write-through caches) have SIZE=32 bytes. The cache coherency protocol is a "write invalidate" protocol, where the cache being written issues a Coherent Invalidate transaction if the line is not exclusive. This indicates to all caches that they should immediately invalidate the line since it will contain "stale data" after the write completes. All caches "snoop" Coherent Read transactions and assert MSH/ if the address of the transaction is present in their cache. By observing MSH/, caches can update the state of the lines they hold. If a cache is the "owner," it asserts the signal MIH/ to tell memory not to send data and then supplies the data to the requesting cache. Coherent Read and Invalidate, and Coherent Write and Invalidate are simply the combination of a Coherent Invalidate with either a Coherent Read or a Write. Their purpose is to reduce the quantity of MBus transactions needed and thus conserve bandwidth. Figure A-2 shows a simplified MBus MP system.

### Definitions

0x-0x as a prefix to a number, indicates that the number is hexadecimal.

MASTER—A module is an MBus master when it "owns" the MBus. Masters assert the signal MAS/ to initiate transactions.

Figure A-2 Standard Level-2 Shared Memory MP

SLAVE—A module is an MBus slave when it responds to transactions directed at it. Slaves assert the signals MRDY/, MRTY/ and MERR/ as an acknowledgment to an MBus master.

BLOCK—A 32 byte data burst transfer size, this quantity is equal to the block (or sub-block) size of the system caches.

TRANSACTION—A transaction is a complete MBus operation such as a Read or Write. It is made up of one address cycle and one or more data acknowledgment cycles. Due to RETRY and RELINQUISH and RETRY acknowledgments a transaction may be repeated many times.

BURST TRANSFER—A multidata-cycle MBus data transfer. MBus allows 16-byte, 32-byte, 64-byte, and 128-byte burst transfers.

BLOCK TRANSFER—A special case of MBus burst transfer, where the data transfer size is equal to the block size (32 bytes).

OWNED—A block of data is said to be owned when there is one (and only one) cache in the system which is responsible for writing it back to memory as well as supplying the block when requested by other caches. If no cache is the owner, memory is considered the owner.

SHARED—A block of data is said to be shared when more than one cache in the system currently possesses a valid copy of it.

EXCLUSIVE—A block of data is said to be exclusive when there is only one cache in the system which contains a valid copy of it.

DIRTY—A block of data is said to be dirty when it has been written to in a write-back cache. Dirty blocks must be written back to main memory if displaced (victimized). A dirty block is "OWNED" by that cache block.

VALID—A block of data is said to be valid when it is present within a processor's cache and can be supplied to that processor upon request. Valid means the cache line is in one of four states: exclusive clean, exclusive dirty, shared clean, or shared dirty.

WRAPPING—This concerns the order in which data will be delivered for multicycle transfers. For MBus, Read transfers larger than 8 bytes require multiple cycles. Wrapping implies that the data to be delivered first is specified by the low order address bits. That is, the transfer address may not be burst size aligned.

#### **Compliance and Additional Features**

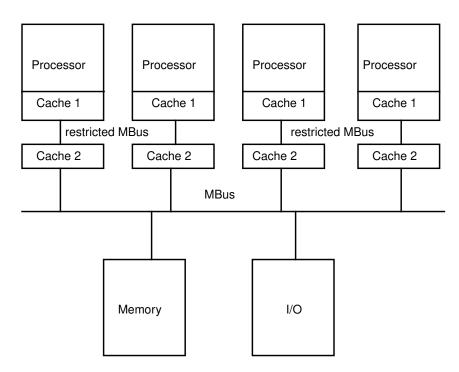

Full compliance with either Level 1 or Level 2 implies a certain minimal functionality within the MBus modules, particularly Level 2 modules where details of the module caches are exposed. Modules may contain more than this level of functionality either to enhance performance, or to enable building a broader range of systems from MBus components. This is at the discretion of module designers and is implementation-specific. An example of a performance enhancement is reflective memory support where memory is updated by observing the data being transferred from cache to cache. An example of functionality enhancement is support for simple second level caches. It is not within the scope of the MBus specification to cover details of these enhancements. MBus is merely a defined set of transactions operating on a defined set of signals. Module enhancements will be covered as "application notes" by module designers and vendors. See Appendix B, "MBus Module Design Guide", for some insight into the nature of the two enhancements mentioned above.

## **Basic Assumptions for Level 2**

| Consistency Quantity       | The data quantity upon which consistency will be maintained will be a cache block or, when implemented, a cache sub-block. It is also assumed that the same (sub-) block size will be used throughout the system and corresponds to the MBus Block size of 32 bytes. |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache Write Policy         | While playing the Level 2 consistency game, all caches in the system will follow a write-back policy with write allocate.                                                                                                                                            |

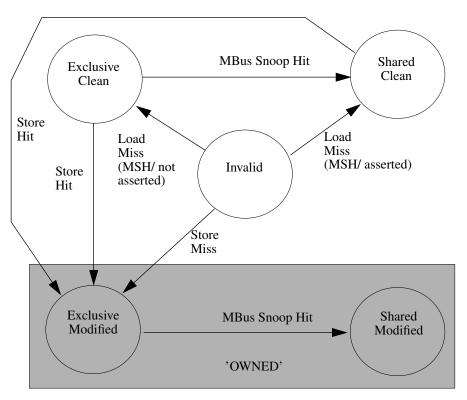

| Cache Consistency Protocol | An ownership-based protocol will be employed. Figure A-3 shows a simplified state transition diagram.                                                                                                                                                                |

Figure A-3 Simplified Cache Block State Diagram

Homogeneous Modules

All modules using the same MBus will play the same consistency game. The modules will appear identical as far as the MBus is concerned, yet they may differ internally.

Second-Level Caches

It is assumed that all second-level caches will be physically addressed.

# **Signal Definition**

## **Physical Signal Summary**

Table A-1 summarizes all the MBus Module physical signals. A slash (/) following the signal name indicates that the signal is active low (true when'0').

| Physical Signals |                         |                 |                 |              |                          |  |

|------------------|-------------------------|-----------------|-----------------|--------------|--------------------------|--|

| Signal<br>Name   | Signal Description      | Output          | Input           | Line<br>Type | Sig<br>Type <sup>a</sup> |  |

| MCLK             | MBus clock              | clock buffer    | Mast./Slv/Arb.  | dedicated    | BS                       |  |

| MAD[63:0]        | Address/Control/Data    | Master/Slave    | Master/Slave    | bussed       | TS                       |  |

| MAS/             | Address strobe          | Mater           | Slave           | bussed       | TS                       |  |

| MRDY/            | Data ready indicator    | SLAVE           | Master          | bussed       | TS                       |  |

| MRTY/            | Xaction retry indicator | Slave           | Master          | bussed       | TS                       |  |

| MERR/            | Error indicator         | Slave           | Master          | bussed       | TS                       |  |

| MSH/             | Shared (level-2only)    | Bus Watcher     | Master          | bussed       | OD                       |  |

| MIH/             | Inhibit (level-2 only)  | Bus Watcher     | Master/Memory   | bussed       | TS                       |  |

| MBR/             | Bus request             | Master          | Arbiter         | dedicated    | BS                       |  |

| MBG/             | Bus grant               | Arbiter         | Master          | dedicated    | BS                       |  |

| MBB/             | Bus busy indicator      | Master          | Arbiter/Master  | bussed       | TS                       |  |

| IRL[3:0]         | Interrupt Level         | Interrupt Logic | CPU Modules     | dedicated    | BS                       |  |

| ID[3:0]          | Module Identifier       | System          | MBus Modules    | dedicated    | BS                       |  |

| AERR/            | Asynchronous error out  | Module          | Interrupt Logic | bussed       | OD                       |  |

| RSTIN/           | Module reset in signal  | Reset Logic     | Master/Slave    | impl depen   | BS                       |  |

| INTOUT/          | Interrupt Out           | I/O Modules     | Interrupt Logic | dedicated    | BS                       |  |

| SCANDI           | Scan Data In            | System          | Modules         | dedicated    | BS                       |  |

| SCANDO           | Scan Data Out           | Modules         | System          | dedicated    | BS                       |  |

| SCANCLK          | Scan Clock              | System          | Modules         | dedicated    | BS                       |  |

Table 3-1. Physical Signal Summary

a. BS = bi-state, TS = tri-state, OD = open drain

### **Physical Signal Descriptions**

MCLK MBus master clock—The distribution of the MCLK signal in a system is implementation-dependent. For example, depending on the connector, each module on the MBus may be given one or more identical MCLK lines which could originate from a single clock generator.

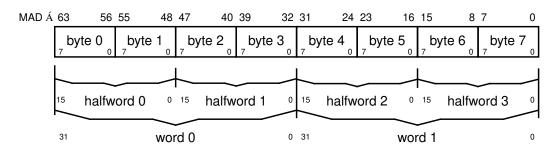

MAD[63:0]—Memory Address and Data. During the address phase, MAD[35:0] contains the physical address (PA[35:0]). The remaining signals (MAD[63:36]) on the bus contain the transaction-specific information which is described in "Multiplexed Signal Descriptions". During the data phase, MAD[63:0] contains the data of the transfer. The bytes are organized as shown in Figure A-4. For transactions involving less than a double word (8-bytes), the data must be aligned. For example, all even-addressed words will be aligned on MAD[63:32] whereas all odd-addressed words will be aligned on MAD[31:0]. As another example, byte address 2 of an odd-addressed word will be carried on MAD[15:8] i.e. byte 6 on the MBus. Unused data lines during the data phase are undefined.

MAS/—Memory Address Strobe. This signal is asserted by the bus master during the very first cycle of a bus transaction. The cycle in which it is asserted is referred to as the "address cycle" or "address phase" of the transaction. For transactions that receive a Relinquish and Retry or a Retry acknowledgment, MAS/ will be asserted again until the transaction gets a normal or error acknowledgment. Other cycle timing is discussed with respect to MAS/. For example, A+2 indicates the second cycle after MAS/ assertion; i.e., MAS/ assertion is A+0.

MRDY/—MBus ready transaction status bit. This bit is one of the three bits used to encode the transaction status as shown in Table A-2. The encoding with MRDY/ asserted alone indicates that valid data has been transferred. The three status bits (MRDY/, MRTY/, and MERR/) are normally asserted by the addressed slave. The ERROR2 (Time-out) acknowledgment will be asserted by the bus monitor.

| Table 3-2. | Transaction Status Bit Encoding |

|------------|---------------------------------|

|------------|---------------------------------|

| MERR/ | MRDY/ | MRTY/ | Meaning               |  |

|-------|-------|-------|-----------------------|--|

| Н     | Н     | Н     | idle cycle            |  |

| Н     | Н     | L     | Relinquish and Retry  |  |

| Н     | L     | Н     | H Valid Data Transfer |  |

| Н     | L     | L     | reserved              |  |

| L     | Н     | Н     | ERROR1=> Bus Error    |  |

| L     | Н     | L     | ERROR2=> Time-out     |  |

MRTY/—MBus retry transaction status bit. This bit is one of the three bits used to encode the transaction status as shown in Table A-2. The encoding with MRTY/ asserted alone indicates that the slave wants the master to abort the current transaction immediately and start over. The master will relinquish bus ownership upon this type of a retry acknowledgment. Note that if any type of acknowledgment other than "Valid Data Transfer" is issued, the cycle it is issued is the last cycle, regardless of how many further acknowledgment cycles would normally occur. The three status bits (MRDY/, MRTY/, and MERR/) are normally asserted by the addressed slave.

MERR/—MBus error transaction status bit. This bit is one of the three bits used to encode the transaction status as shown in Table A-2. The encoding with MERR/ asserted alone indicates that a bus error (or other system implementation specific error) has occurred. Note that if any type of acknowledgment other than "Valid Data Transfer" is issued, the cycle it is issued is the last cycle, regardless of how many further acknowledgment cycles would normally occur. The three status bits (MRDY/, MRTY/, and MERR/) are normally asserted by the addressed slave.

MBR/—MBus Request signal. This signal is asserted by an MBus master to acquire bus ownership. There is one unique MBR/ signal per master.

MBG/—MBus Grant signal. This signal is asserted by the external arbiter when the particular MBus master is granted the bus. There is one unique MBG/ signal per master.

MBB/—MBus busy signal. This signal is asserted as an output during the entire transaction, from and including the assertion of MAS/ to the assertion of the last MRDY/ or first other acknowledgment which terminates the transaction (such as an error acknowledgment). If a master wishes to keep the bus and perform several transactions without releasing the bus between them, it keeps MBB/ asserted until the last MRDY/ of the last transaction of the group. The potential master device samples this signal in order to obtain the bus ownership as soon as the current master releases the bus. MBB/ locks arbitration on a particular MBus. A master is allowed to assert MBB/ prior to the assertion of MAS/ (to hold the bus). It is also allowed to keep MBB/ asserted after the assertion of the last acknowledgment in a few special cases for performance reasons. This continued assertion of MBB/ should only occur while MBG/ is still parked on the current master. The MAS/ of the transaction prompting the continued assertion of MBB/ should be generated quickly (2 cycles is the recommended maximum delay). For more details on arbitration see "Arbitration Protocol" in Chapter 4.

MIH/—Memory InHibit signal. This signal is only present in level-2 MBus modules. It is asserted by the owner of a cache block at the beginning of the second cycle after it receives the address (its A+2 cycle)<sup>1</sup> to inform the Main Memory that the current Coherent Read or Coherent Read and Invalidate request should be ignored. This is because the owner, not the Memory, will be responsible for delivering the cache data block. If no device asserts MIH/ during its A+2 cycle, main memory will be responsible for delivering the data. If main memory starts delivering data and MIH/ is asserted, the memory delivery shall be aborted immediately. Any data which was received from main memory in this case should be ignored. It should be noted that because of the restriction on MIH/ either occurring simultaneously with or before MRDY/, there will be at most two cycles worth of data to ignore. While MIH/ is sourced by a module (for one cycle) two cycles after receiving MAS/ it may be observed by a cache in the interval from its A+2 until it observes an acknowledgment. This variation in where MIH/ can be observed is due to the possibility for MBus repeaters and modules that do not meet the A+2 timing.

MSH/—Cache block SHared signal (wired-or, open-drain). This signal is only present in level-2 MBus modules. Whenever a Coherent Read transaction appears on the bus, the bus monitor of each processor module should immediately search its cache directory. If a valid copy is found, the MSH/ signal should be asserted in the second cycle after the address is received (its A+2 cycle). The MSH/ signal is also sampled (observed) by external caches. It is asserted as an output (for a single cycle) if there is a cache hit in the snooping directory. While MSH/ is sourced by a module two cycles after receiving MAS/ it may be observed by a cache from its A+2 until it observes an acknowledgment. This variation in where MSH/ may be observed is due to the possibility for MBus repeaters and modules that do not meet the A+2 timing. Signals are sourced at the beginning and observed or sampled at the end of a cycle. Due to the open drain nature of MSH/ and the associated slow rise time, while the signal is driven active low for one cycle, it can be observed active low for up to two cycles, and the trailing or rising edge of the signal is considered asynchronous.

RSTIN/—Module reset input signal. This signal should reset all logic on a module to its initial state, and ensure that all MBus signals are inactive or tri-state as appropriate. The minimum assertion time of RSTIN/ will be system implementation dependent, although the default assertion time will be 1024 MBus clock (MCLK) periods (25.6 microseconds). RSTIN/ should be treated as asynchronous.

AERR/—Module asynchronous error detect out signal. This signal is asserted by the module as a level to indicate that an asynchronous error was detected by the module. It remains asserted until a software-initiated action resets a bit that is maintaining the signal assertion. AERR/ is open drain because several modules could assert it simultaneously. AERR/ may be asynchronous.

INTOUT/—Module Interrupt out signal. This signal is asserted by an I/O module as a level to indicate an interrupt request to the system. It remains asserted until a software initiated action resets a bit that is maintaining the signal assertion. INTOUT/ may be asynchronous. This signal is optional.

IRL[3:0]—These pins carry the Interrupt Request level inputs to a SPARC Integer Unit. They are only used by processor modules. IRL[3:0] may be asynchronous. Each processor module receives a dedicated set of IRL[3:0].

<sup>1.</sup> See Appendix B for notes to designers who wish to avoid the A+2 requirement.

ID[3:0]—These pins carry the Module Identifier. These signals are not needed by Level 1 processor modules, which have a default ID of 0xF, and are optional for other modules who may obtain this information by other means. ID[3:0] is reflected as MID[3:0] during the address phase of every transaction, and is also used to identify a unique address range for Module identification, initialization and configuration.

If modules do not have ID[3:0] input pins, the system must provide a function that allows each module to obtain a unique ID[3:0] value in an internal ID[3:0] register. One way this can be accomplished is to have a logic function with a known MBus address attached to the MBus arbiter. There are unique MBR/ and MBG/ lines per module and so this function when addressed, would return a unique ID[3:0] value on MAD, based on which module's MBG/ was asserted just prior to the beginning of the ID Read transaction when MBB/ was de-asserted.

SCANDI—This signal corresponds to the signal TDI as described in IEEE P1149.1 (hereafter referred to as P1149). It is an input to the module and is used for receiving scan data from the system. This is the input of the scan ring and should not be inverted or gated. This signal changes on the falling edge of SCANCLK and should be sampled on the rising edge of SCANCLK. Scan is optional.

SCANDO—This signal corresponds to the signal TDO as described in P1149. It is an output of the module and is used for sending the scan data to the system. This is the output of the scan ring and should not be inverted or gated. SCANDO should be driven on the falling edge of SCANCLK and will be sampled on the rising edge of SCANCLK. Scan is optional.

SCANCLK—This signal is used to supply the clock to the scan ring on the module. (Typically 5 MHz) Scan is optional.

SCANTMS1—This signal is an input to the module. It is used to control the TAP controller state machine. It corresponds to the TMS signal as described in P1149. Scan is optional.

SCANTMS2—This signal is an input to the module. It is used to reset the TAP controller state machine. It corresponds to the TRST/ signal as described in P1149. Scan is optional.

# **Multiplexed Signal Summary**

Table A-3 summarizes the multiplexed MBus signals. All multiplexed signals are active high (true when'1').

| Multiplexed Signals (valid during address phase) |                                                                                                                                  |  |  |  |  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Physical Signal                                  | Signal Description                                                                                                               |  |  |  |  |

| MAD[35:0]                                        | Physical address for current transaction                                                                                         |  |  |  |  |

| MAD[39:36]                                       | Transaction type                                                                                                                 |  |  |  |  |

| MAD[42:40]                                       | Transaction data size                                                                                                            |  |  |  |  |

| MAD[43]                                          | Data cacheable (advisory)                                                                                                        |  |  |  |  |

| MAD[44]                                          | Bus lock indicator (advisory)                                                                                                    |  |  |  |  |

| MAD[45]                                          | Boot mode/local bus (advisory)(optional)                                                                                         |  |  |  |  |

| MAD[53:46]                                       | Virtual address (optional)(level-2)                                                                                              |  |  |  |  |

| MAD[58:54]                                       | reserved for future expansion                                                                                                    |  |  |  |  |

| MAD[59]                                          | Supervisor Access Indicator (advisory)(optional)                                                                                 |  |  |  |  |

|                                                  | Physical Signal<br>MAD[35:0]<br>MAD[39:36]<br>MAD[42:40]<br>MAD[43]<br>MAD[43]<br>MAD[44]<br>MAD[45]<br>MAD[53:46]<br>MAD[58:54] |  |  |  |  |

# **Multiplexed Signal Descriptions**

PA[35:0]—Physical address of current transaction which is multiplexed on MAD[35:0].

TYPE[3:0]—The transaction types are encoded in bits MAD[39:36] as shown in Table A-4. Most of the transaction types are reserved.

| TYPE[3] | TYPE[2] | TYPE[1] | TYPE[0] | Data Size | Transaction Type                 |

|---------|---------|---------|---------|-----------|----------------------------------|

| Н       | Н       | Н       | Н       | -         | reserved                         |

| Н       | Н       | Н       | L       | -         | reserved                         |

| Н       | Н       | L       | Н       | -         | reserved                         |

| Н       | Н       | L       | L       | -         | reserved                         |

| Н       | L       | Н       | Н       | -         | reserved                         |

| Н       | L       | Н       | L       | -         | reserved                         |

| Н       | L       | L       | Н       | -         | reserved                         |

| Н       | L       | L       | L       | -         | reserved                         |

| L       | Н       | Н       | Н       | -         | reserved                         |

| L       | Н       | Н       | L       | -         | reserved                         |

| L       | Н       | L       | Н       | 32B       | Coherent Read & Invalidate(CRI)  |

| L       | Н       | L       | L       | any       | CoherentWrite & Invalidate (CWI) |

| L       | L       | Н       | Н       | 32B       | Coherent Read(CR)                |

| L       | L       | Н       | L       | 32B       | Coherent Invalidate(CI)          |

Table 3-4. TYPE Encoding (as defined by the SIZE signals in Table A-5)

SIZE[2:0]—The transaction data SIZE information is encoded in bits MAD[42:40]. The size field is encoded as log<sub>2</sub> [number of data bytes transferred]. The encoding of the SIZE bits is shown in Table A-5.

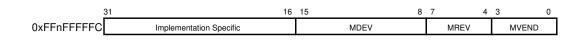

For transactions with SIZE greater than 8 bytes, more than one MRDY/ will be needed. For read transactions, MBus supports a feature called "wrapping." During the address phase, MAD[2:0] are don't care, and MAD[35:3] defines the 8 bytes to be returned with the first MRDY/. This means that the address defines which data to return first, and this will vary. Data returned on subsequent MRDYs will be for the address associated with incrementing MAD[n:3] where n = 3 for SIZE = 16-bytes, n = 4 for SIZE = 32-bytes, up to n = 6 for SIZE = 128-bytes. As the address is (conceptually) incremented, the MAD[n:3] field will wrap around without incrementing MAD[35:n+1], which is static for the duration of transaction.

Wrapping affects all modules that have to deliver data with SIZE greater than 8 bytes. An exception is Level 2 cache controllers, which may choose not to support wrapping for snoop read hits, when they supply the data. This means that Level 2 processor modules that don't support wrapping on the snoop port cannot share an MBus with Level 2 MBus processors that issue "wrapped" requests. To ensure maximum compatibility, Memory and I/O modules should all support wrapped requests to their slave ports, but should only issue aligned requests from their master ports.

The wrapping feature is not supported for writes. Write transactions with SIZE greater than 8 bytes should have address bits MAD[n:3] be zero, and MAD[2:0] are undefined as for reads.

For transactions with SIZE less than or equal to 8 bytes, unneeded address lines are undefined. e.g. for SIZE = 8 bytes, MAD[2:0] are undefined.

| SIZE[2] | SIZE[1] | SIZE[0] | Transaction Size      |

|---------|---------|---------|-----------------------|

| L       | L       | L       | Byte                  |

| L       | L       | Н       | Half-word (2 bytes)   |

| L       | Н       | L       | Word (4 bytes)        |

| L       | Н       | Н       | Double-word (8 bytes) |

| Н       | L       | L       | 16-byte Burst         |

| Н       | L       | Н       | 32-byte Burst         |

Table 3-5. SIZE Encoding

VA[19:12]—Virtual Address 19 through 12 (multiplexed on MAD[53:46]). This field only applies to MBus level-2 Coherent transactions. It is used to carry the virtual address bits 19 through 12 associated with the physical address of a Coherent Read transaction. These bits are used by virtually indexed caches that desire to index into the dual directories via the virtual "superset" bits to avoid synonym problems. This assumes a minimum page size of 4K in the system and maximum cache size of 1MB. Modules that choose not to provide this function nor to support non-coherent transactions (such as a level-1 device) should drive these lines high.

MID[3:0]—Module identifier signals (multiplexed on MAD[63:60]). This field is sourced by all MBus modules and reflects the value input into the module on the ID[3:0] input signals. For level-1 processor modules this field is driven high(0xF). This field is observed by slave ports that wish to issue a Relinquish and Retry acknowledgment, so that they can identify the master with which to reconnect in a multimaster system configuration.

C—Cacheable indicator (multiplexed on MAD[43]). When this signal is asserted, it indicates the state of the cacheable bit for the address of the transaction in the module MMU (if there is one). If a module has insufficient information to determine the level of this bit for a transaction, it should leave the bit de-asserted. This is an advisory bit, not used by MBus transactions, but possibly of use to the slave device.

An example use of C would be to inform a second level cache of the cacheability state of the address of a transaction with SIZE less than 32 bytes.

LOCK—Lock indicator signal (multiplexed on MAD[44]). If the MBus master intends to lock access to a device residing on MBus (main memory is one MBus device) or some other bus connected to MBus, and perform N indivisible MBus transactions to the device, this bit needs to be asserted during the address cycles of all N MBus transactions. The locking master must keep MBB/ asserted during each locked cycle and not de-assert it until the end of the final locked transaction (however MBB/ may be suspended for a time by an R&R acknowledgment). The de-assertion of MBB/ signals the MBus arbiter to release the MBus. It is the final de-assertion of MBB/ after possible intervening R&R acknowledgments which tells the device to release its lock. LOCK is an advisory bit, not used by MBus transactions directly, but possibly of use to the slave device or bus interface.

An example use of LOCK would be to "lock" an MBus master to a particular slave. If an MBus processor performed an atomic operation to a resource arbitrated externally to MBus, such as a dual-ported memory device or another bus, then the external arbiter could prevent any other (non MBus) device from accessing that resource by locking arbitration. The referenced slave device in a LOCKed transaction could be, in essence, dedicated to the requesting master. The MBus slave port interface interprets an assertion of the MBus LOCK bit as saying "become locked" and a final de-assertion of MBB/ at the end of the locked sequence as saying "become unlocked", and reports this information to the arbiter for the "locked" device (or bus). If the slave port supports R&R acknowledgments, it must know not to clear the locked state when MBB/ is removed due to an R&R.

MBL—MBus boot mode / local bus indicator (multiplexed on MAD[45]). This signal is asserted by processor modules during the address phase of boot mode transactions, or during local bus transactions (SPARC processor accesses with ASI = 0x1). It is system implementation-dependent whether or not local bus transactions are employed in a system. This is an advisory bit, not used by MBus transactions, but possibly of use to the slave device. This bit is optional. If unused by an implementation it should remain de-asserted.

SUP—Supervisor access indicator (multiplexed on MAD[59]). This signal is asserted by processor modules and indicates that the MBus transaction is a processor Supervisor access. This is an advisory bit, not used by MBus transactions, but possibly of use to the slave device. This bit is optional. If unused by an implementation, it should remain asserted.

An example use of SUP would be to enable more state to be captured on processor asynchronous write errors.

reserved—This 5-bit field (multiplexed on MAD[58:54]), is reserved for future MBus expansion. The lines should be driven high if not used.

# **MBus Transactions**

### **Semantics**

- 1. Basic cycle is read/write (size), where size is from 1 to 128 bytes.

- 2. Bus cycles greater than 8 bytes are performed as bursts.

- **3.** Data rate is controlled by the slave. Master must be able to accept a burst read, or source a burst write, of requested size, at maximum transfer rate.

- 4. Master starts bus cycle with MAS/ (address transfer phase). Master also asserts MBB/ at (or before) this time.

- **5.** In the case of burst mode, multiple acknowledgments are used and the bus cycle ends with the acknowledgment of the last data transfer. The master de-asserts MBB/ at end of the last cycle (except for locked bus cycles).

- **6.** Locked bus cycles are an indivisible sequence of basic bus cycles. Locked cycles are also terminated immediately by error acknowledge and individual transactions in the sequence may be suspended by retry or relinquish and retry acknowledgments.

**Note** – In the transaction semantic diagrams that follow, optional wait states are indicated as x, y, or z cycles. x, y, and z can be zero.

# Level 1 Transaction Types

#### Read

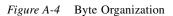

A Read operation can be performed on any size of data transfer which is specified by the SIZE bits in Figure A-5. Read transactions support wrapping as defined in section 2.4. Read transactions involving less than 8 bytes will have undefined driven data on the unused bytes. The minimum MBus Read transaction will take 2 cycles. This minimum time is for the cases when no data is returned on MAD, such as during R&R or error acknowledgments. If data is being returned, an extra cycle is required to avoid bus contention. The arbitration protocol creates a dead cycle between transactions which ensures there will be no bus contention between backto-back reads from different masters. If a module locks the bus and performs back-to-back reads, it is its responsibility to ensure a dead cycle to avoid contention Note that the protocol means that a master must be able to receive data at the maximum rate of the MBus for the duration of the transaction, i.e. 8 bytes on every consecutive clock. Figure A-5 depicts the semantics of a Read operation. Refer to Chapter 8 for details pertaining to cycle waveforms.

#### Write

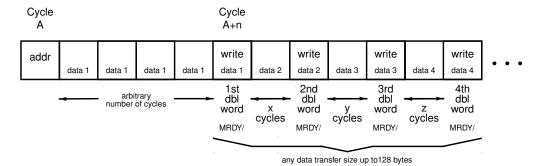

A Write operation can be performed on any size of data transfer which is specified by the SIZE bits in Figure A-6. Write transactions involving less than 8 bytes will have undefined data on the unused bytes. The writing master will immediately drive the data in the period after the address phase of the transaction, and immediately after receipt of each MRDY/ in transactions with SIZE greater than 8 bytes. Note that the protocol means that a master must be able to source data at the maximum rate of the MBus for the duration of the transaction, i.e., 8 bytes on every consecutive clock. The minimum MBus Write operation will take 2 cycles (minimum is actually 3 cycles if different masters are performing back-to-back writes). Figure A-6 shows the basic semantics of a Write operation.

#### Figure A-6 Write Semantics

Due to the nature of the cache-consistency protocol, the Write transaction works equally well in Level 1 and Level 2 MBus implementations. Writes can be used for non-cacheable accesses as well as for write-backs of dirty (sub-)blocks. Write transactions do not need to be snooped and the MIH/ and MSH/ signals must not be asserted during the operation.

R&R acknowledgments issued to Block Write transactions to cacheable locations introduce a detailed design problem, in that the write-back buffer in this case may be the only source of the most up to date data. This introduces the prospect of having to snoop the write back buffer. To simplify the design of processor modules, the MBus specification eliminates the need for processor modules to snoop write-back buffers and places the burden of handling this case of R&R acknowledgment on the module that issues the R&R. Modules that issue R&R acknowledgments to cacheable block write transactions must capture the address(es) of the cache line(s) until they complete the transaction to which they issued R&R. Should other modules attempt to read the line(s) during this interval the R&R issuing module must detect this and issue R&R to the intervening Coherent Read(CR) or Coherent Read and Invalidate(CRI) transaction(s). In general it should be possible for most modules to avoid the need to issue R&R to cacheable block write operations and hence avoid this complexity. The only likely exception is a coherent bus adaptor.

### Additional Transaction Types for Level 2

#### **Coherent Read**

A Coherent Read operation is a block read transaction that maintains cache consistency. The participants in the transaction are the requesting cache, the other caches which snoop, and memory (or a second level cache). There are three possible read scenarios which the caches that snoop can experience:

- 1. For a snooping cache which does not have a copy of the requested block, it simply ignores this transaction.

- **2.** For a snooping cache which does have a copy of the requested block but does not own it, it simply asserts MSH/ for one cycle during its cycle  $A+2^1$ . It will mark its copy as shared (if not already marked as such).

**3.** For a snooping cache which owns the requested block, it will assert both the MSH/ and MIH/ signals for one cycle during bus cycle A+2 and start shipping the requested data no sooner than its cycle A+6, (4 cycles after it issued MIH/). If its own copy of the block was labeled exclusive, it will be changed to shared, else no status change will take place for its own copy.

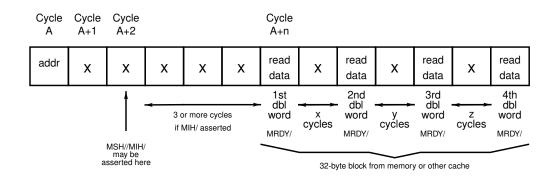

Upon receiving the data block, the requesting master shall label the block exclusive if no one asserts MSH/ during its cycle A+2 and shared if the signal MSH/ is asserted during its cycle A+2. Figure A-7 depicts the semantics of a Coherent Read operation where memory latency is long.

Case (c) above needs further elaboration. This is the only case where MIH/ is asserted. This signal affects three parties. It is sourced by the snooping (intervening) cache and observed by both memory (or a second level cache) and the requesting cache. It tells the requesting cache that it may have received stale data from memory, and to ignore that data and data it may receive on the next clock and wait until the fourth or later clock for the correct data. It tells memory to stop sending data immediately, which means memory may send one more MRDY/ before it can stop. The delay of 4 clocks at the requesting cache and the snooping (intervening) cache serve two related purposes. The first is to allow time for MRDY/ and MAD from the memory to be turned off before the snooping cache asserts MRDY/ and MAD, and so avoid bus contention. The second is to allow for implementations that buffer the MBus.

The earliest that memory (or a second level cache) is allowed to issue MRDY/ (or any acknowledgment) is its cycle A+2. This ensures that acknowledgments never occur before MIH/. Figure A-7 shows the semantics of a Coherent Read transaction.

#### **Coherent Invalidate**

An Invalidate operation can only be performed on a block basis. All Invalidate operations will be snooped. If an Invalidate operation hits in a cache, then that copy will be invalidated immediately, regardless of its state. One module (normally a memory controller) is responsible for the acknowledgment of the Coherent Invalidate transaction. This is accomplished on its cycle A+2 or later. All acknowledgment types are possible. Memory will only ever issue normal acknowledgments (MRDY/) to Coherent Invalidates, but coherent bus adaptors may issue other acknowledgments, particularly R&R. It should also be noted that a Coherent Invalidate transaction will have SIZE = 32B during the address phase, but it will only be expecting one MRDY/ for the acknowledgment. Also the address may not be 32-byte aligned. Memory (or coherent bus adaptor) designers should take note of this. If in a particular system, caches cannot guarantee to complete their invalidation before their A+2 cycle, the memory controller for that system should delay the acknowledgment as appropriate. This implies that memory controllers should have a feature that allows the time to acknowledge invalidates to be varied to some extent, either hardwired or through a programmable register. A recommended range for the programmable delay is A+2 to A+10. This programmable delay is the MBus flow control technique to guarantee that invalidates can be completed at any rate they are issued.

<sup>1.</sup> See Supplement B for notes to designers who wish to avoid the A=2 requirement.

Figure A-7 Coherent Read Semantics

This Coherent Invalidate MBus transaction is issued when a write is being performed into a cache line that is Shared. Before the write can actually be performed, all the other systems caches must have their local copies invalidated (write-invalidate cache-consistency protocol). Snooping caches will not assert MSH/ during A+2. The MAD lines will contain undefined data during the data phase cycles. If a Coherent Invalidate transaction should receive an R&R acknowledgment there is a possibility that the line which is about to be written becomes invalidated by an intervening invalidation transaction on the bus. This means that when the cache regains the bus it should issue a Coherent Read and Invalidate transaction, not a Coherent Invalidate transaction, to once again allocate the (sub-)block. Figure A-8 shows the basic semantics of an Invalidate operation.

For any particular system, selecting which module will be responsible for acknowledging Coherent invalidates introduces some issues for memory controller designers. In most systems a single memory controller will be responsible. In systems with a coherent bus adaptor, the adaptor will be responsible. If it is desired to use a memory controller in a system that also has a coherent bus adaptor, it is then required to be able to tell the memory controller not to respond to invalidates. This should be accomplished during system initialization prior to enabling any caches, preferably by writing a bit in a register in a memory controller.

Figure A-8 Coherent Invalidate Semantics

#### **Coherent Read and Invalidate**

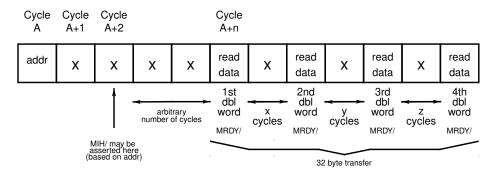

Since the MBus supports a write-invalidate type of cache-consistency protocol, a special Coherent Read and Invalidate transaction, which combines a Coherent Read transaction with a Coherent Invalidate transaction, was included to reduce the number of MBus transactions. Caches that are performing Coherent Reads with the knowledge that they intend to immediately modify the data can issue this transaction.

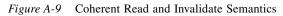

Each Coherent Read and Invalidate transaction will be snooped by all system caches. If the address hits and the cache does not own the block, then that cache will immediately invalidate its copy of this block, no matter what state the data was in. If the address hits and the cache owns the block, then it will assert MIH/ and supply the data. When the data has been successfully supplied, the cache will then invalidate its copy of this block. Figure A-9 shows the basic semantics of a Coherent Read and Invalidate operation. Note that it is identical to the Coherent Read operation, except that the system caches will invalidate the block. All of the detailed comments concerning MIH/ for the Coherent Read transaction apply equally to the Coherent Read and Invalidate transaction.

#### **Coherent Write and Invalidate**

A Coherent Write and Invalidate transaction combines a Write transaction with a Coherent Invalidate transaction. The Coherent Write and Invalidate transaction is intended to reduce the number of MBus transactions. This transaction can be used by Level-2 modules that wish to support a write through cache, a degree of functionality beyond the requirements for level-2 MBus. (Supporting write through caches is useful for implementing simple 2nd level caches that support inclusion.) CWI is also of use to block copy and block fill mechanisms.

Each Coherent Write and Invalidate transaction will be snooped by all system caches. If the address hits, then caches will invalidate their copies of this block no matter what state the data was in. Figure A-10 shows the basic semantics of a Coherent Write and Invalidate operation. Note that it is identical to the Write operation, except that the system caches will invalidate the block. All SIZE values are allowed and a single 32-byte block is invalidated regardless of the value of SIZE. Due to the nature of the cache coherency protocol neither MIH/ nor MSH/ is asserted.

All SIZE values are allowed in order to better accommodate write through caches. Systems with only either write through or write back caches work naturally, but a system with both a write through and a write back cache are very unlikely to work in a way that preserves cache consistency. This mixed system is not anticipated or recommended as a real MBus configuration.

Figure A-10 Coherent Write and Invalidate Semantics

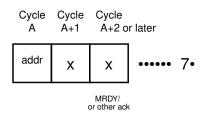

### **Acknowledgment Cycles**

It is a requirement that any transaction once issued must correctly accept any acknowledgment type. This applies to all Level 1 and Level 2 transactions. The earliest that an acknowledgment can be issued is A+1 for Read and Write and A+2 for all Coherent Transactions. Processor caches that are supplying data as part of a Coherent Read transaction may only issue either normal or error acknowledgments. They may not issue R&R or Retry acknowledgments.

#### **Idle Cycles**

When there is no bus activity or when it is necessary to insert wait states in between the address cycle and the data cycle or between consecutive data cycles, an addressed slave can simply refrain from asserting any transaction status bits (MERR/, MRDY/, and MRTY/). The number of wait cycles which can be inserted is arbitrary, as long as it does not exceed the system time-out interval (see "Acknowledgment Cycles" for time-out details).

#### Relinquish and Retry (R&R)

When a slave device cannot accept or supply data immediately, it can perform a relinquish and retry acknowledgment cycle by asserting MRTY/ for only one bus cycle. This will indicate to the requesting master that it should release the bus immediately so that the bus can be re-arbitrated and possibly used by another MBus master. This involves at least one dead cycle until the suspended transaction can be performed in the case when the bus is still granted to the re-trying master. When the bus is no longer granted to the master in question, then the suspended transaction must wait until bus ownership is once again attained. When a transaction that receives an R&R acknowledgment regains bus mastership it must issue the same transaction over from the beginning. An exception to this is when a Coherent Invalidate turns into a Coherent Read and Invalidate (see "Coherent Invalidate"). For Level 1 modules, for all transactions with SIZE greater than 8 bytes, a relinquish and retry acknowledgment can be asserted on any data transfer. For Level 2 modules, for all transactions with SIZE greater than 8 bytes, (including the Level-1 READ and WRITE transactions) R&R can only be issued on the first acknowledgment. It is the responsibility of the slave port to time the duration of the transaction that is causing it to issue R&R, and return an ERROR2 acknowledgment to the correct master when its device specific time-out interval (200 micro-seconds is recommended) has passed and the master has reconnected to the slave.

There are two different cases that cause slaves to issue R&R acknowledgments. The first is slow devices. If a device is slow to respond, the slave interface should wait a short interval (around one microsecond is recommended), and then issue an R&R acknowledgment. It should also capture the ID of the master from the MAD lines during the address phase (MID[3:0] field) and enter a "port busy" state while waiting for the device attached to the slave to respond. The master will eventually reconnect and the R&R process will be repeated until either the device responds or the slave time-out interval (which should be much greater than the short interval, 200 microseconds is recommended) is exceeded. The slave will then issue the normal or error acknowledgment respectively and exit the "port busy" state.

In systems with multiple masters, the slave that issues R&R must capture the ID of the master whose transaction is being postponed in order to know which master should receive the normal or error acknowledgment when the slave can complete the transaction. If a master with an ID other than that captured by the slave port should access the slave port while it is in the "port busy" state, it should simply be given an R&R acknowledgment.

The second cause of R&R acknowledgments is the resolution of deadlock situations where there are a master and a slave port sharing an MBus interface and simultaneous transactions on both ports requires one transaction to back off. R&R requires the current owner of MBus to relinquish ownership in order to resolve the deadlock. R&Rs used to resolve deadlocks are inherently stateless and do not require a "port busy" state.

A detail of significance is that R&R can be issued to a transaction that is part of a locked sequence of transactions. By definition, all transactions in a locked sequence are addressed to the same device, e.g., main memory (or second-level cache) or an I/O adapter. There is only one "port busy" state per device, so there is only one source of R&R for a locked sequence.

Normally, main memory will not issue R&R. Multiple R&R sources from main memory would restrict locked sequences to addresses within one memory bank, Also, some aspects of coherent cache design are simplified by locking some MBus sequences such as fills and their associated write-back (if any). These sequences rely on either a memory system that does not issue R&R or an appropriately designed second level cache or coherent bus adaptor that does. For more details see "Level 1 Transaction Types".

It should be noted that processor caches which assert MIH/ and then supply data cannot issue R&R acknowledgments.

#### Valid Data Transfer

A valid or ready data transfer is indicated by a responding slave with the assertion of the MRDY/ transaction status bit for only one cycle. This signal needs to be asserted on reads to indicate to the requesting master that valid data has just arrived. On writes, MRDY/ indicates to the writing master that the data has been accepted and that the writing master shall stop driving the accepted data. The next double-word, if a write burst was being performed, will be driven onto the bus in the cycle immediately following the assertion of MRDY/.

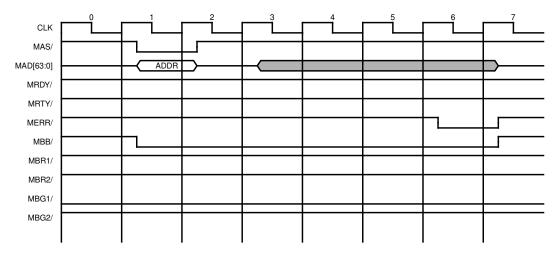

#### ERROR1 => Bus Error

When the responding device asserts only the MERR/ transaction status bit, the requesting master will interpret this as an external bus error just having taken place. The meaning of "Bus Error" is implementation-dependent.

#### ERROR2 => Time-out

This acknowledgment is expected to be generated by some sort of watchdog timer logic in the system that primarily detects transactions that are not acknowledged. This is accomplished by timing the shorter of either the assertion of MBB/ or the time since the last MAS/ assertion, as follows.

A time-out counter should start on the assertion of MBB/ and count until the de-assertion of MBB/, or until the timer has counted the time-out interval. If the counter counts to the time-out limit, a time-out error acknowledgment should be generated by the time-out monitor circuitry. When counting ceases, the counter should be reinitialized to its initial condition. If MAS/ is asserted during the time that counting is enabled (MBB/ assertion) the counter should be reinitialized, but continue counting. The number of cycles for the time-out interval is system implementation-dependent. An interval of 200 microseconds is recommended. This error code can also be used to indicate a system implementation dependent error. Time-out is the suggested interpretation of an ERROR2 acknowledgment.

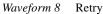

#### ERROR3 => Uncorrectable

This acknowledgment is mainly used by the addressed memory controller to inform the requester that in the process of accessing the data some sort of uncorrectable error has been encountered (like parity, uncorrectable ECC, etc.). This error code can also be used to indicate a system implementation-dependent error. Uncorrectable error is the suggested interpretation of an ERROR3 acknowledgment.

#### Retry

This acknowledgment differs from the Relinquish and Retry acknowledgment in that the master will not, in this case, release bus ownership if it is no longer granted the bus, but rather the transaction will immediately begin again with an address phase (MAS/, etc.) as soon as the retried master is ready to do so. Retry errors can occur on any acknowledgment of a transaction. This type of acknowledgment can be useful when a correctable ECC error has occurred in the main memory subsystem.

Should a Retry acknowledgment occur on other than the first acknowledgment cycle, the issue of "Data Correctness" arises. Modules that use delivered data prior to completion of the transaction may not be able to tolerate delivery of bad data. They may choose to treat Retry acknowledgments as equivalent to ERROR3 acknowledgments. This assumes that the Retry is "stateless" and the slave device issuing it will not hang or otherwise malfunction if the transaction is not retried. This is a detail at the discretion of system implementors.

#### Reserved

This acknowledgment is reserved for future use. Should a master receive a Reserved acknowledgment its behavior is undefined.

# Arbitration

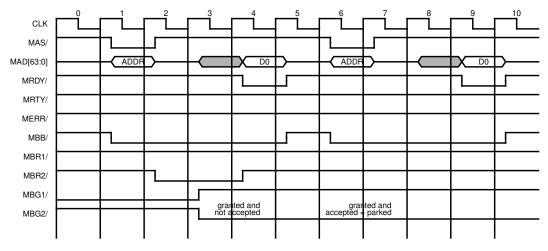

# **Arbitration Principles**

- The Arbiter is a separate unit from both the slave(s) and master(s).

- Arbitration is overlapped with current bus cycle.

- Back-to-back transactions by different masters are not allowed. There must be at least one dead cycle in between each transaction during which MBB/ is de-asserted.

- Arbitration algorithm is implementation dependent. (Fair bandwidth allocation should be maintained.)

- Bus parking will be employed. (Current master keeps the bus until it is taken away by another request.)

- Locked cycles are accommodated to handle indivisible operations.

# **Arbitration Protocol**

The MBus arbitration scheme assumes a central arbiter. The exact algorithm used by the arbiter (like round-robin, etc.) is implementation-dependent.

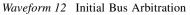

### **Bus Requestors**

A requesting module requests the MBus by asserting its dedicated MBR/ signal and then waits for assertion of its dedicated grant signal MBG/ by the arbiter. Upon receiving its dedicated grant signal (MBG/), the requesting master can start using the bus by asserting MAS/ and MBB/ as soon as MBB/ is released (de-asserted) by the previous master. It is not necessary for the requesting master to assert MAS/ immediately, but it is necessary to assert MBB/ to acquire and hold the bus. A requesting master is not guaranteed to gain bus ownership if it does not immediately assert MBB/ upon detecting the condition of its MBG/ asserted and MBB/ de-asserted because if some other master is requesting the bus, the arbiter will then assert the grant to the new requestor.

The requestor, upon receiving its dedicated grant signal (MBG/) should immediately remove its dedicated request (MBR/) on the next clock edge. It is allowed to assert MBR/ in anticipation of needing the bus, and then deassert it prior to receiving MBG/. However, this may waste bus cycles and should be avoided.

### **Bus Arbiter**

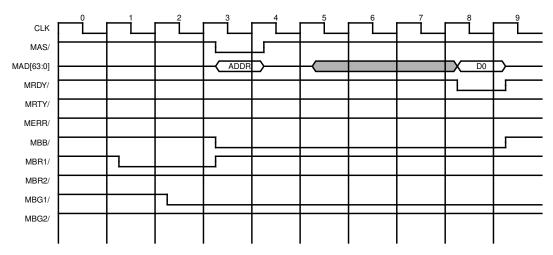

The arbiter uses only the MBRn/, MBGn/, signals from each master and the common bussed MBB/ signal. The arbiter receives the requests (MBR/n) and resolves which grant (MBG/n) to assert. A grant remains asserted until at least one cycle after the current master has de-asserted MBB/ when it becomes "parked," and may be removed at any time after this in response to assertion of further requests. If no other requests (MBR/n) are asserted, the grant (MBG/n) remains asserted (parked). Only one grant (MBG/) is asserted at any time. A dead cycle between successive transactions of different masters will always occur with the MBus arbitration scheme. See "Timing Diagrams" for example transactions.

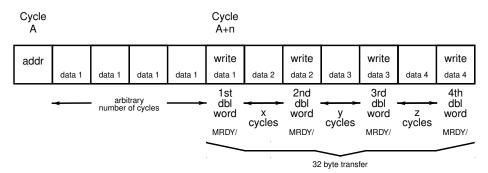

Figure A-11 shows a block diagram and a state diagram of an arbiter that resolves two requests and issues the two associated grants. In the state diagram, the state names are indicated in bold text within the state circles. The signal outputs associated with each state are indicated in normal text within the state circles. In the state transition equations, ! indicates NOT, & indicates AND and # indicates OR. The signals are represented in their positive logic form. The reset signal MRST is omitted from the state transition equations for clarity. For larger arbiters, the state transition diagram becomes more complex. There will always be two states per MBG signal, one for the case where a grant has been issued but not accepted, and the other for the case where the grant has been (potentially) accepted and the arbiter remains parked on that grant.

Figure A-11 Example of a Two-Grant MBus Arbiter

# **MBus Configuration Address Map**

A small portion of the MBus memory space has been preallocated to each potential MBus module, to allow for a uniform method of system configuration. There is an individual space per MBus ID, 16 spaces in total. The ID of a module is determined by the value on the ID[3:0] pins. Level 1 processor modules do not have slave interfaces and so will not respond at the configuration address map locations. Table A-6 shows the configuration address spaces of MBus.

| Table 3-6. | MBus | Configuration | Address | Мар |

|------------|------|---------------|---------|-----|

|------------|------|---------------|---------|-----|

| Configuration Spaces |                 | MBus Identifier               |  |

|----------------------|-----------------|-------------------------------|--|

| 0xFF0000000          | to 0xFF0FFFFFF  | Range for ID=0x0 <sup>a</sup> |  |

| 0xFF1000000          | to 0xFF1FFFFFF  | Range for ID=0x1              |  |

| 0xFF2000000          | to 0xFF2FFFFFF  | Range for ID=0x2              |  |

|                      |                 |                               |  |

|                      |                 |                               |  |

|                      |                 |                               |  |

| 0xFFF000000          | to 0xFFFFFFFFFF | Range for ID=0xF              |  |

a. reserved for "boot prom"

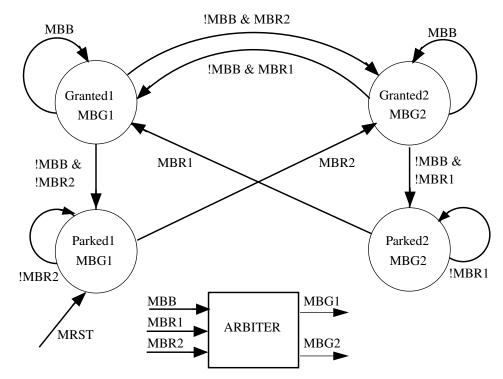

One 32-bit location in each space (0xFFnFFFFC where n=ID) is fixed and should contain the Implementation Number and Version Number of the MBus module in an MBus Port Register (MPR) which is shown in Figure A-12. A processor accessing the 16 possible MPRs can determine what ID slots are present (through time-out) and

what devices they contain from the contents of the MPR. Other than this one address, the use of the address range is implementation-specific and specified by module vendors. Examples of items located in these configuration address ranges are registers that determine the address ranges which memory and I/O modules respond to. Similarly, implementation-specific registers and memories necessary to configure and test modules would reside at locations within the device-specific configuration address space.

Figure A-12 MBus Port Register Format

MDEV—MBus Device number. This field contains a unique number which indicates the vendor-specific MBus device that is present at the referenced MBus port. Refer to Vendors for their MDEV assignments.

MREV—Device Revision number. This field contains a number that can be interpreted as a revision number or some other variable of a device. Refer to Vendors for their MREV assignments, if any.

MVEND—MBus vendor number. This field contains a unique number which indicates the vendor of the device present at the referenced MBus port. Refer to Supplement A for current MVEND assignments.

On coming out of reset, processor modules will fetch instructions from MBus address 0xFF000000 and subsequent memory locations. This means that the configuration address space for ID=0x0 is special and always needs to be present. MBus ID=0x0, then, can be considered as the "boot PROM" MBus module.

# **MBus Electrical Characteristics**

# **MBus Electrical Principles**

Bus Protocol-The MBus is a fully synchronous bus. The frequency of operation is 40 Mhz.

Sampling—All signals are changed and sampled on rising clock edges.

Driver Overlap—No bussed signal is driven in the same cycle by more than one source. All bussed control signals (except MSH/ and AERR/ which are open-drain) follow a sequence from tri-state to active low to driven high to tri-state, normally on successive rising clock edges. Since MBB/ can be driven by two sources with only one dead cycle in between, the drive high followed by tri-state must occur within a single cycle. The multiplexed address data bus signals (MAD) follow a sequence from tri-state, to active high or low, to tri-state. MAD lines should always be high or low before tri-stating to ensure MAD lines are always at a known logic level.

Noise—To avoid noise problems due to "floating" signals or very slow rise time signals, high impedance holding amplifiers are required on the MAD lines. Bussed control lines require high impedance pull-up resistors. These amplifiers and/or resistors are a centralized function, provided by the system.

Driver Turn On—There are many cases in the protocol where it is necessary to turn on and drive a signal in the same clock cycle. It is a general assumption that this is also done even for cases where it is not absolutely necessary. Care needs to be taken where a driver is turned on before the signal is driven as the protocol does not define the cases where this may be possible. This is particularly true for CR and CRI which are three party transactions.

# **Signal Grouping**

For timing purposes, signals are divided into four groups, MAD[63:0], bussed control, point-to-point control and misc. (See Figure A-13) Bussed control includes MAS/, MRDY/, MERR/, MRTY/, MBB/, MSH/, and MIH/. Point-to-point control includes MBR/ and MBG/. Misc. includes RSTIN/, IRL[3:0], INT-OUT/, and AERR/.

| SIGNAL CLASS            | SIGNAL                                      |

|-------------------------|---------------------------------------------|

| BUSSED CONTROL:         | MAS/, MRDY/, MRTY/, MERR/, MBB/, MSH/, MIH/ |

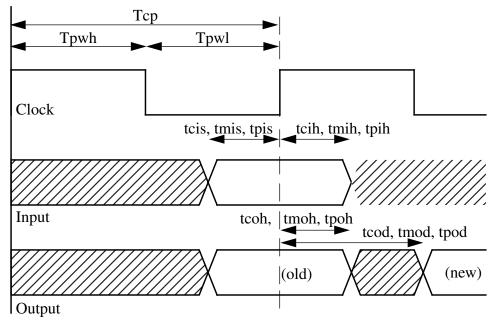

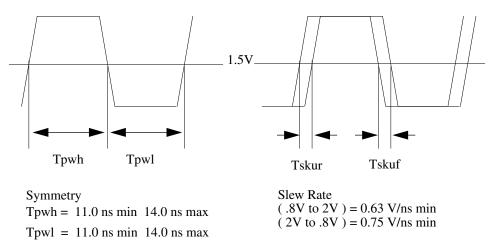

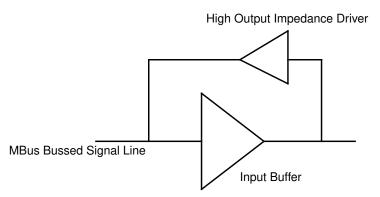

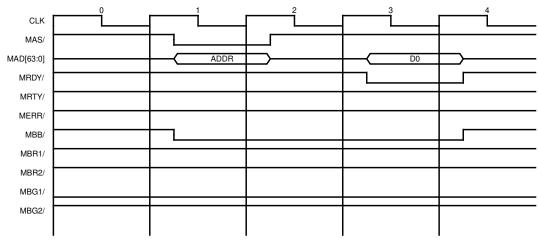

| POINT-TO-POINT CONTROL: | MBR/, MBG/                                  |